Дешифраторы И Шифраторы Rating: 8,3/10 3439reviews

Дешифраторы и шифраторы Микросхемы комбинационного типа средней степени интеграции Справочник по микросхемам ТТЛ и КМОП Любительская Радиоэлектроника Дешифраторы и шифраторы. Из микросхем комбинационного типа при разработке цифровых устройств широко используют дешифраторы, их номенклатура довольно разнообразна. S, объединенных по И, и 1. Если на обоих входах стробирования лог. Если хотя бы на одном из входов стробирования S лог. Из двух микросхем ИДЗ, дополненных одним инвертором, можно собрать дешифратор на 3. ИДЗ и двух инверторов (рис 8.

ИДЗ (рис 8. 2). Такая структура микросхемы позволяет использовать ее в различных вариантах включения. На основе микросхемы ИД4 могут быть построены, в частности, дешифраторы на восемь выходов со входом стробирования (рис 8. Если дополнить микросхему ИД4 тремя элементами 2. И- НЕ, можно получить дешифратор на десять выходов (рис.

ИД4, но имеет выходы с открытым коллектором. В ряде случаев, например при двоично- десятичном представлении чисел, удобно использовать неполные дешифраторы, в которых число выходов меньше числа возможных состояний адресных входов.

Подписывайтесь на нашу группу Вконтакте — http:// и Facebook — https://www.facebook.com/chipidip * Шифратор - это .

На основе полного дешифратора всегда можно построить неполный на меньшее число входов. Дешифратор имеет четыре входа, которые могут подключаться к выходам любого источника кода 1- 2- 4- 8, и десять выходов, которые могут подключаться к катодам газоразрядного цифрового или знакового индикатора (анод последнего через резистор сопротивлением 2. Ом подключен к полюсу источника постоянного или пульсирующего напряжения 2. В). 1. 9) или декады по рис. И, в качестве которого могут быть использованы два любых маломощных диода (рис. ЛИ1. 0 не более 2,5 В, что превышает порог переключения микросхем ТТЛ, составляющий около 1,3 В.

Шифратор (кодер) — (англ. Здесь вы узнаете, зачем нужны шифраторы и дешифраторы в цифровой электронике. Также показан пример работы дешифратора на . К основным комбинационным устройствам относят дешифраторы, шифраторы, мультиплексоры (распределители), демультиплексоры и сумматоры. Шифратор (кодер) — (англ. М., Аргус, 1993, ISBN 5-85549-004-1 · Методические указания. Исследование комбинационных схем. Дешифратор (декодер). Шифратор (кодер).

Практически выходное напряжение микросхем К1. ИД1 в состоянии 0 может быть несколько выше или ниже порога переключения, поэтому для надежной работы микросхемы- нагрузки в минусовую цепь питания этой микросхемы следует включить кремниевый диод. Кроме того, поднимется выходной уровень лог. В, что вполне достаточно для нормальной работы последующих микросхем. К1. 55. ИД1 с микросхемами ТТЛ.

Как и микросхема К1. ИД1, она имеет четыре адресных входа 1,2,4,8, но ее десять выходов 0- 9 выполнены по стандартной схеме. S, два из которых инверсные, и восемь инверсных выходов. S - на инверсных входах должен быть лог. При всех других сочетаниях сигналов на входах S на всех выходах микросхемы - лог.

Три микросхемы ИД7 можно объединить в дешифратор на 2. DD1 - DD3 на рис. Дополнив схему рис. ИД7 и инвертором, можно получить дешифратор на 6. К5. 55. ИД6, но с выходами, выполненными с открытым коллектооом. А, в состоянии лог. В. Для микросхемы К1.

Дешифраторы и шифраторы. Из микросхем комбинационного типа при разработке цифровых устройств широко используют дешифраторы, . Логические устройства разделяют на два класса: комбинационные и последовательностные. Устройство называют комбинационным, если его .

ИД1. 0 максимально допустимое напряжение, которое можно подвести к выходу, находящемуся в состоянии лог. В. Выходное напряжение лог. А не более 0,4 В, при токе 8. А - не более 0,9 В. Указанные выходные параметры позволяют применять микросхему К1. ИД1. 0 при построении распределителей с релейными выходами (рис.

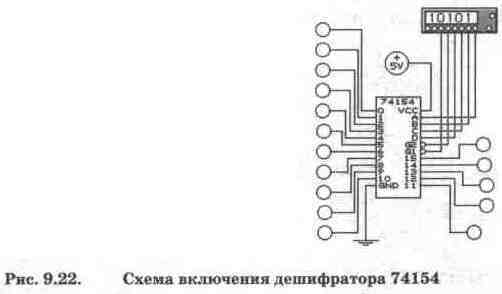

Для примера на рис. К1. 55. ИД1, К5. 55. ИД6. 9. 7) содержит два стробируемых дешифратора, каждый с двумя адресными входами 1 и 2, инверсным входом стробирования S и инверсными выходами 0- 3. S лог. 0 появляется на том выходе дешифратора, номер которого соответствует десятичному эквиваленту двоичного числа, поданному на адресные входы 1 и 2.

S на всех выходах дешифратора также лог. Она имеет восемь информационных входов 0- 7 и вход разрешения Е. Выходов у микросхемы пять - три инверсных выходного кода 1,2,4; G - признака подачи входного сигнала и Р - переноса.

G - лог. 1, на выходе Р - лог. При подаче лог. 0 на любой из информационных входов 0- 7 на выходах 1,2, 4 появится инверсный код, соответствующий номеру входа, на который подан лог. Р - лог. 1, которая запрещает работу других микросхем ИВ1 при их каскадном соединении. Если же на входе Е лог. DD3 появятся младшие разряды прямого выходного кода, на выходе G DD1 - лог. Телефонный Справочник Г.Навои.

Р - лог. 1, являющаяся признаком подачи входного сигнала. Р DD2 запретит работу DD1, младшие разряды на выходах DD3 определяются микросхемой DD2, на выходе 8 выходного кода будет лог. В этом случае выходы переноса микросхем с большими номерами следует соединить со входами запрета микросхем с меньшими номерами, выходы 1, 2,4 следует через многовходовые элементы И- НЕ подключить к выходам устройства - это будут младшие разряды выходного кода. Выходы G микросхем ИВ1 следует соединить с входами 0- 7 еще одной микросхемы ИВ1, с выходов которой можно будет снять старшие разряды кода и признак подачи входного сигнала G (рис. В схемах рис. 1. 00 и 1. Она имеет девять инверсных входов 1- 9 для подачи кодируемого сигнала и четыре инверсных выхода кода 1- 2- 4- 8. В исходном состоянии на всех входах и выходах лог.

При подаче на любой из входов лог. Для примера на рис. Если нажать любую из 1.

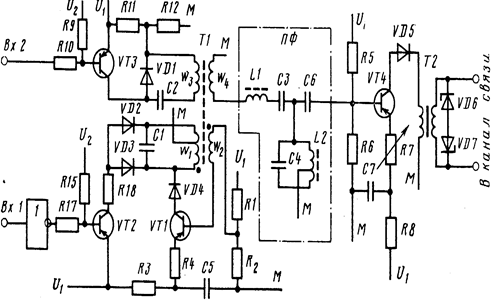

SB1 - SB1. 0, на выходе микросхемы DD1 сформируется инверсный код нажатой кнопки (для кнопки SB1 - 1. DD2. Ток через один из резисторов R1 - R1. VT1, на его коллекторе появится лог. На выходе элемента DD3. DD3. 2 - лог. Изменение напряжения на правой обкладке конденсатора передается на вход элемента DD3.

DD3 в противоположное состояние (рис. Изменение лог. 0 на выходе элемента DD3.

DD1 в триггеры микросхемы DD2, на ее инверсных выходах появится прямой код нажатой кнопки. DD3. 1, вся цепочка элементов микросхемы DD3 переключится. На время дребезга контактов кнопки лог. DD3,1 будет поддерживаться за счет положительной обратной связи через конденсатор С2. На выходе микросхемы DD2 сохранится код нажатой кнопки. Если при нажатой кнопке нажать еще одну, выходной код не изменится, он будет соответствовать первой из нажатых кнопок.

Код не изменится и при отпускании кнопок. Если нажать одновременно (с точностью до задержки, вносимой цепью подавления дребезга DD3. DD3. 2) две или более кнопок, выходной код будет соответствовать кнопке с большим номером. ИВ1, в этом случае транзистор VT1 излишен. Входной сигнал на схему подавления дребезга необходимо будет подать с выхода G микросхемы ИВ1.